Arquitectura de Sistemas de Cómputo

Semestre:

3°Fecha de elaboración:

Agosto de 2013Fecha de revisión:

Septiembre de 2013Elaborado por:

Juan Manuel Rendón, Jorge Hermosillo ValadezCiclo de formación:

BásicoÁrea curricular:

Ciencias de la DisciplinaTipo de unidad:

TeóricaCarácter de unidad:

ObligatoriaClave:

AC01FB050010Créditos:

10Semestre:

3°Horas Teoría:

5Horas Práctica:

0Programas académicos en los que se imparte:

Licenciatura en Ciencias Áreas terminales en Matemáticas, Física, Bioquímica y Biología Molecular, y Ciencias Computacionales y Computación CientíficaPrerrequisitos:

Comprende los conceptos básicos del diseño de circuitos lógicos y su importancia en el diseño de la arquitectura de la computadora, a utilizar expresiones matemáticas para describir funciones combinatorias simples y circuitos secuenciales. Diseña un circuito simple utilizando circuitos lógicos y las herramientas matemáticas para la simplificación de fórmulas lógicas.Antecedentes Recomendadas:

NingunaConsecuentes Recomendadas:

- Sistemas Operativos

- Redes de Computadoras

Presentación de la unidad de aprendizaje:

Proporciona el conocimiento de la estructura y organización de las computadoras digitales recientes. Este conocimiento le permitirá al estudiante escribir sus programas de una manera que pueda aprovechar mejor la máquina de la que dispone.

Propósito de la unidad de aprendizaje:

Introducir al estudiante a la organización y arquitectura de los sistemas de cómputo, desde el modelo inicial de Von Neuman hasta los modelos de arquitecturas más recientes.

Competencias profesionales:

Domina los conceptos y la terminología básica de la computación.

Contribución al perfil de egreso:

Para el cumplimiento del perfil, se desarrolla la habilidad para enlazar conocimientos y técnicas de diferentes áreas de las ciencias exactas y naturales.

Secuencia temática:

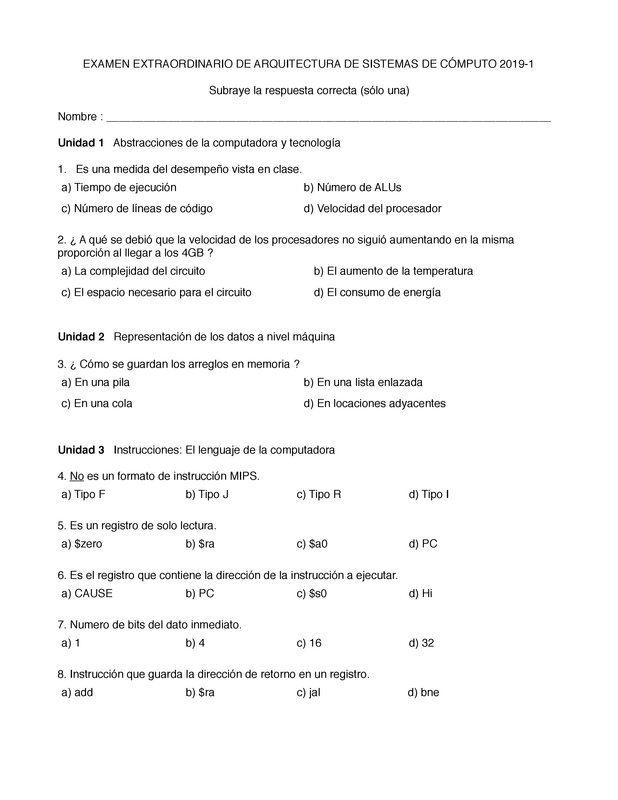

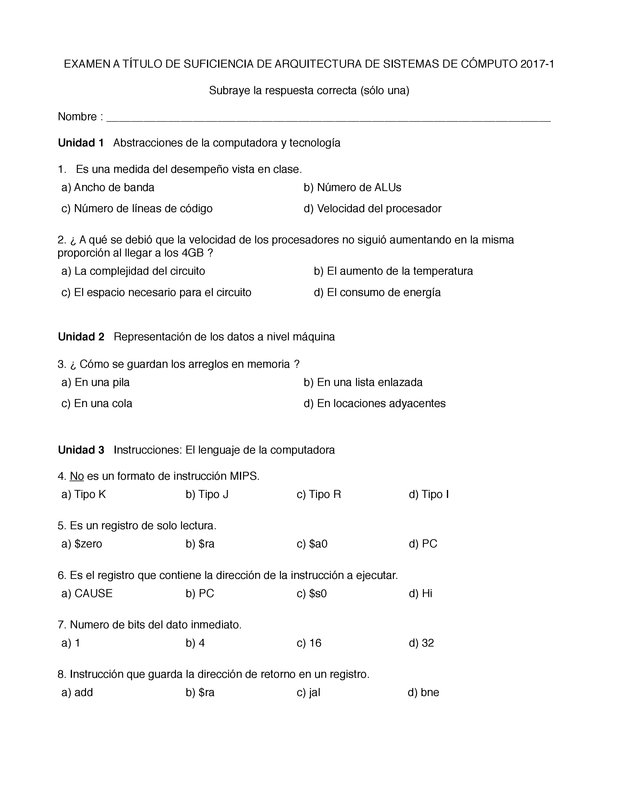

- I Abstracciones de la computadora y tecnología.

- Introducción. ¿Qué hay bajo tu programa? Lenguaje de programación de alto nivel, función del compilador, programa en lenguaje máquina binario.

- Bajo la cubierta. Esquema general de la organización de una computadora: los cinco componentes principales de la computadora: entrada, salida, memoria, bus de datos (datapath) y unidad de control. Ejemplos de dispositivos de entrada y de salida. Descripción breve de la tarjeta madre, la memoria RAM, la CPU (que se compone del bus de datos y la unidad de control) y dispositivos de almacenamiento.

- Desempeño. Ancho de banda (throughput o bandwidth). Tiempo de ejecución. Medición del desempeño.

- El cambio de uniprocesadores a multiprocesadores. Ejemplos de máquinas de la última década.

- II Representación de los datos a nivel máquina.

- 2.1 Bits, bytes y palabras. Representación de datos numéricos y números base. Sistemas de punto fijo. Representación del signo y del complemento.

- 2.2 Operaciones lógicas.

- 2.3 Representación de datos no numéricos (códigos de caracteres, datos gráficos).

- 2.4 Representación de registros y arreglos.

- III Instrucciones: el lenguaje de la computadora.

- 3.1 Operaciones del hardware de la computadora. Ejemplos de operaciones.

- 3.2 Operandos del hardware de la computadora. Registros, variables (operandos en memoria), constantes (operandos inmediatos).

- 3.3 Conjunto de instrucciones MIPS y tipos de instrucciones (manipulación de datos, control, entrada/salida). Lenguaje de programación ensamblador. Formato de las instrucciones (formato-R, formato-I y formato-J). Modos de direccionamiento (inmediato, de registro, de direccionamiento de desplazamiento, de direccionamiento relativo el PC y de direccionamiento pseudodirecto). Llamadas a subrutinas y mecanismos de retorno. Entrada/salida e interrupciones.

- 3.4 Paralelismo e instrucciones: sincronización. Bloquear y desbloquear memoria. Intercambio atómico.

- 3.5 Traducción e inicio de un programa. Descripción de la jerarquía de traducción para el lenguaje C: 1) Compilación, 2) Ensamblado, 3) Enlazado y 4) Cargado en memoria. Librerías de enlazado dinámico.

- IV Aritmética para computadoras.

- 4.1 Suma y resta.

- 4.2 Multiplicación. Multiplicación en serie.

- 4.3 División.

- 4.4 Paralelismo y aritmética de computadora: asociatividad.

- V El procesador.

- 5.1 Unidad de control, instrucción fetch, decodificación y ejecución.

- 5.2 Construyendo el bus de datos.

- 5.3 Un esquema de implementación simple.

- 5.4 Unas visión general a la canalización (pipelining).

- 5.5 Bus de datos y control canalizados.

- 5.6 Problemas de datos: forwarding versus stalling.

- 5.7 Problemas del control.

- 5.8 Excepciones.

- 5.9 Paralelismo y paralelismo a nivel de instrucción avanzado.

- VI Organización y arquitectura de los sistemas de memoria.

- 6.1 (Opcional). Sistemas de almacenamiento y su tecnología. Almacenamiento externo, organización física y controladores (drivers).

- 6.2 Jerarquía de la memoria. Organización de la memoria principal y operaciones. Retardos, tiempo del ciclo, ancho de banda e intercalado. Memorias caché (asignación de la dirección, tamaño del bloque, reemplazo y políticas de almacenamiento). Memoria virtual. Manejo de fallas y seguridad.

- 6.3 Paralelismo y jerarquía de memoria: coherencia de caché.

- VII Interfaz y comunicación.

- 7.1 Fundamentos de entrada/salida: (handshaking, bufering, entrada/salida programada, entrada/salida manejada por interrupciones). Estructuras de interrupción: vectorizadas y priorizadas, interrupción conocida.

- 7.2 Buses: protocolos, arbitraje, memoria de acceso directo (DMA).

- 7.3 Opcional. Introducción a las redes de trabajo.

- 7.4 Opcional. Suporte multimedia.

- 7.5 Opcional. Arquitecturas RAID.

- VIII Opcional. Multinúcleo, multiprocesadores y clusters.

- 8.1 La dificultad de crear programas para procesamiento en paralelo.

- 8.2 Multiprocesadores con memoria compartida. Memoria de acceso uniforme, memoria de acceso no uniforme y sincronización.

- 8.3 Clusters y otros multiprocesadores de paso de mensajes.

- 8.4 Hardware multihilo.

- 8.5 SISD, SIMD, MIMD, SPMD y Vector. Introducción a las GPUs.

- 8.6 Introducción a las topologías de las redes de trabajo de multiprocesador.

Criterios de Evaluación:

- Exámenes parciales: 40%

- Examen final: 30%

- Participación en clase: 10%

- Búsqueda de información: 10%

- Otra (especifique): Tareas: 10%

Bibliografía básica:

- Patterson, David A. y Hennessy, John L. Computer organization and design. Ed. Morgan Kaufmann.

Bibliografía complementaria:

- Hennessy, John L. y Patterson, David A. Computer architecture, a quantitative approach. Ed. Morgan Kaufmann.